随着集成电路制造工艺下探亚5纳米技术节点,传统的晶体管尺寸微缩路线无法像过去一样使“器件-芯片”性能提升并控制成本。

“在此背景下,学术界与工业界近年来提出多种创新器件技术,以期克服常规金属氧化物半导体场效应晶体管(MOSFET)的技术局限。”西安电子科技大学郝跃院士团队刘艳教授介绍,“其中,三星、IBM、欧洲微电子中心(IMEC)等国际研发机构推出了垂直输运场效应晶体管(vertical-transport field-effect transistor, VTFET)器件技术。”

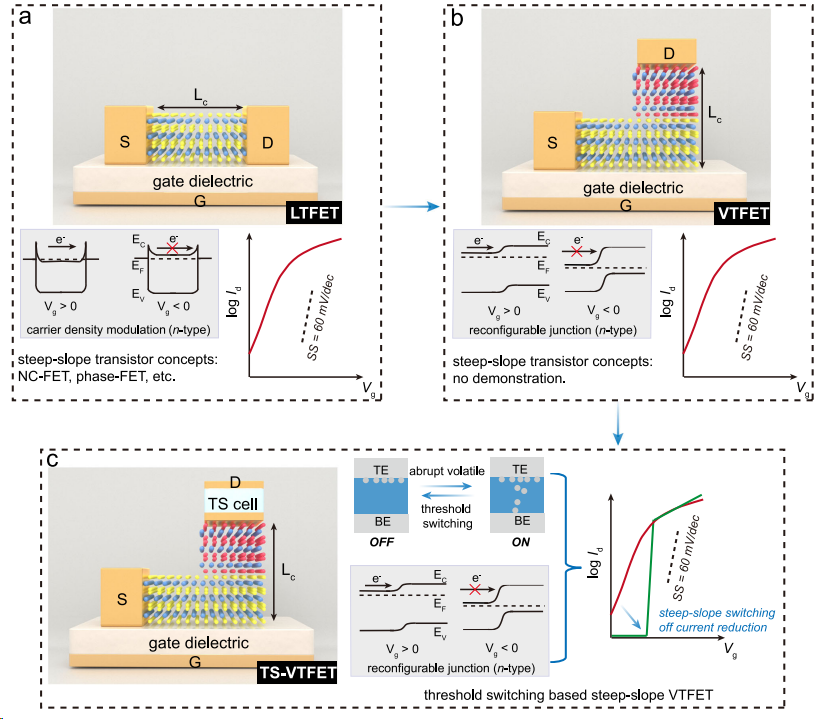

这一技术通过将电流从传统MOSFET的平面方向转换为垂直方向,使该器件结构有望在芯片上垂直构造晶体管,从而大幅降低器件占有空间,提高集成密度。

受此启发,刘艳教授和罗拯东副教授采用超薄二维异质构造VTFET半导体沟道并与电阻阈值开关(TS)垂直集成,实现超陡垂直晶体管(TS-VTFET)。

这一器件技术借助超薄二维半导体出色的静电调控,在大幅提升器件栅控能力的同时,借助电阻阈值开关的电压控制“绝缘-导电”相变特性,使该器件的室温亚阈值摆幅达到1.52mV/dec,远低于常规MOSFET室温亚阈值摆幅高于60mV/dec的理论极限。此外,在发表的概念验证工作中,该研究团队制备的超陡垂直晶体管表现出强大性能,包括电流开关比高于8个数量级、亚60mV/dec电流区间超过6个数量级、漏电流小于10fA等,为后摩尔时代高性能低功耗晶体管技术提供了一种新的方案。以上相关研究成果近日发表于《自然-通讯》上。

超陡垂直晶体管器件结构及其电学性能。作者论文图片

文章相关信息:https://doi.org/10.1038/s41467-024-45482-x

版权声明:凡本网注明“来源:中国科学报、科学网、科学新闻杂志”的所有作品,网站转载,请在正文上方注明来源和作者,且不得对内容作实质性改动;微信公众号、头条号等新媒体平台,转载请联系授权。邮箱:shouquan@stimes.cn。